1、 文檔目標

解決由于絲印重疊導致的制造設計(DFM)問題。

2、 問題場景

絲印重疊阻焊的影響有如下:

1)PCB板后期打樣,一般是以阻焊層優先,如果絲印跟焊盤重疊,那么就會優先選擇焊盤,重疊在焊盤上的絲印就會被消除。

2)絲印附在焊盤上會影響后期的焊接,焊盤表面上會被蓋上油墨,存在絕緣作用影響后期上錫。

Atium Designer 23.6 開始引入”絲印制備“的功能,為整個PCB設計上快速精確定位絲印。避免大量的手動操作和未被檢查到的問題。

3、軟硬件環境

1)、軟件版本:Altium Designer 23.6 以上支持

2)、電腦環境:Windows 11

3)、外設硬件:無

4、解決方法

PCB 封裝庫

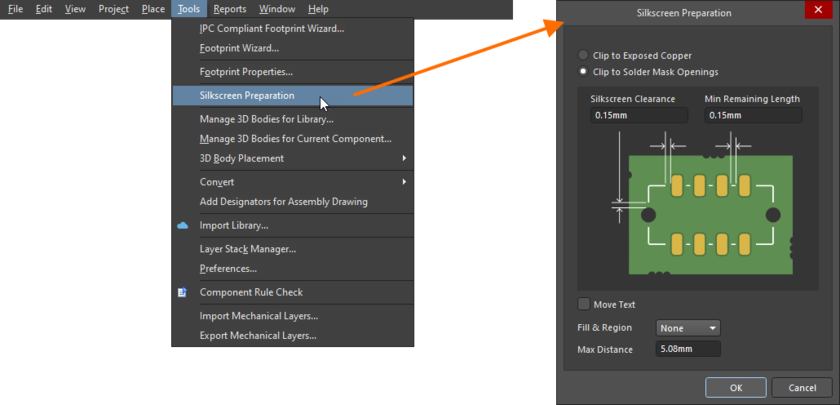

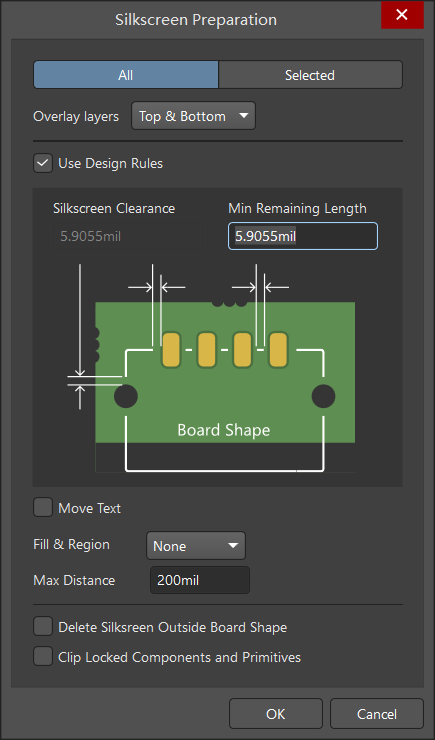

菜單欄下打開:【Tools】→【Silkscreen Preparation】,將絲印制備對話框打開。

圖 1

Clip to Exposed Copper/Clip to Solder Mask Openings :勾選根據銅層裁剪或者阻焊層裁剪,根據制作要求設置裁剪間距;

Move Text:在有文本字符串情況下,進行勾選。可以將絲印文本字符串從銅層/阻焊層重疊移開。移動受【Max Distance】值的約束。

Fill & Region :在有Fill & Region情況下,可以選擇三種模式:

1、None 不做處理;2、Clip 進行裁剪;3、Move 進行移動,受【Max Distance】值的約束。

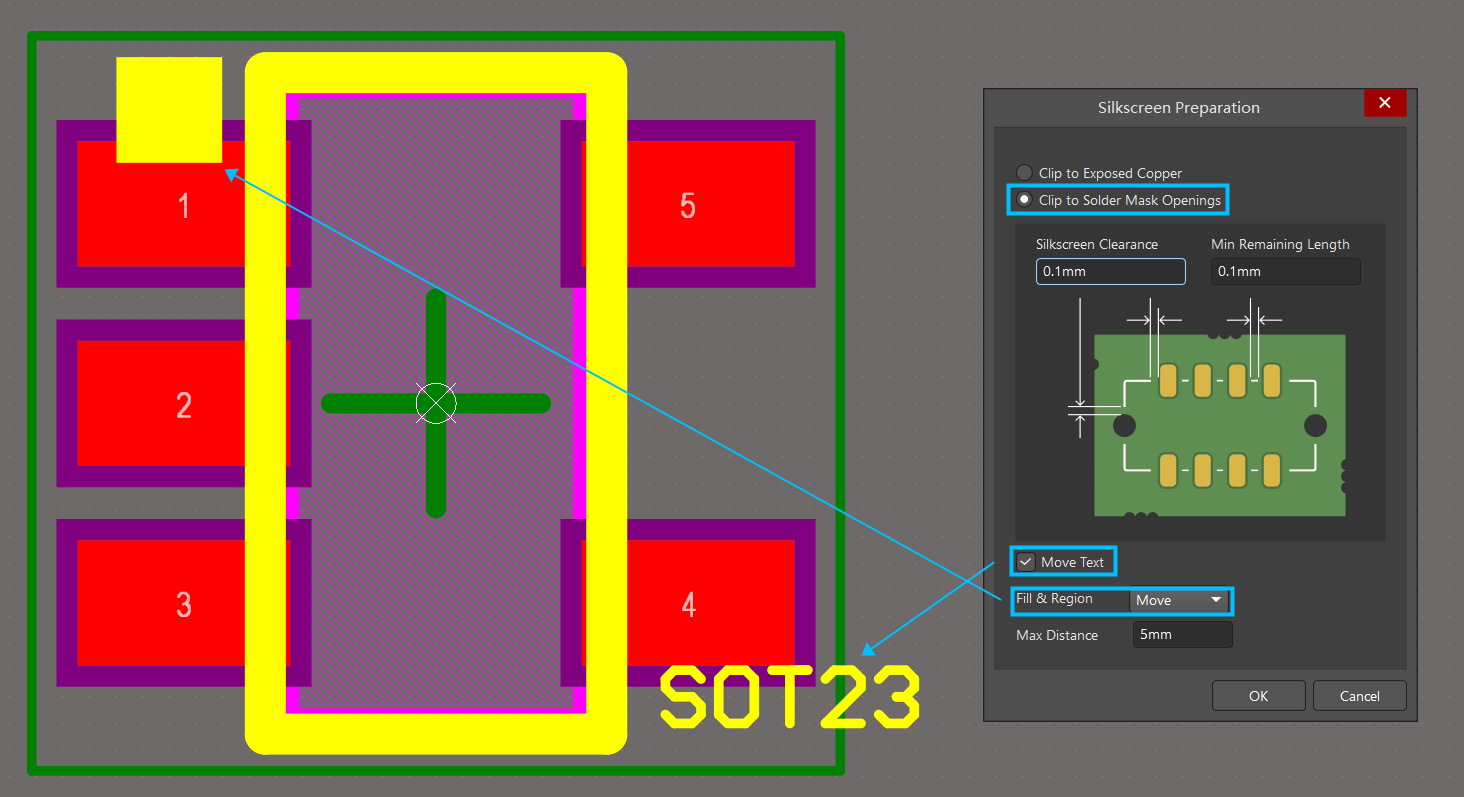

圖 2

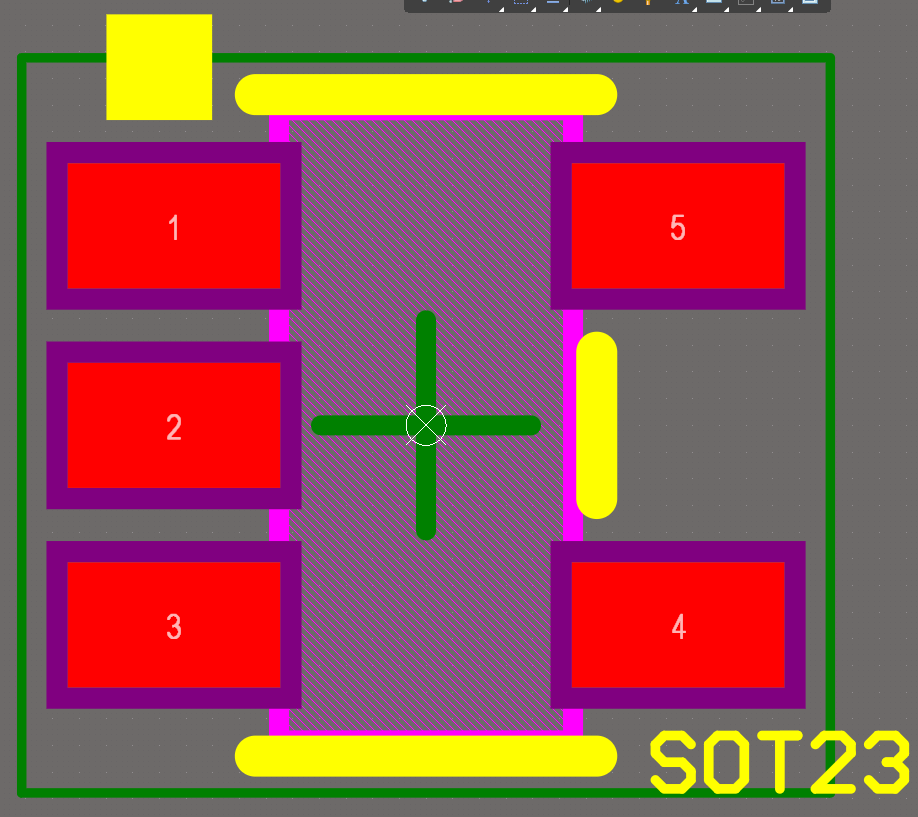

效果如下

圖 3

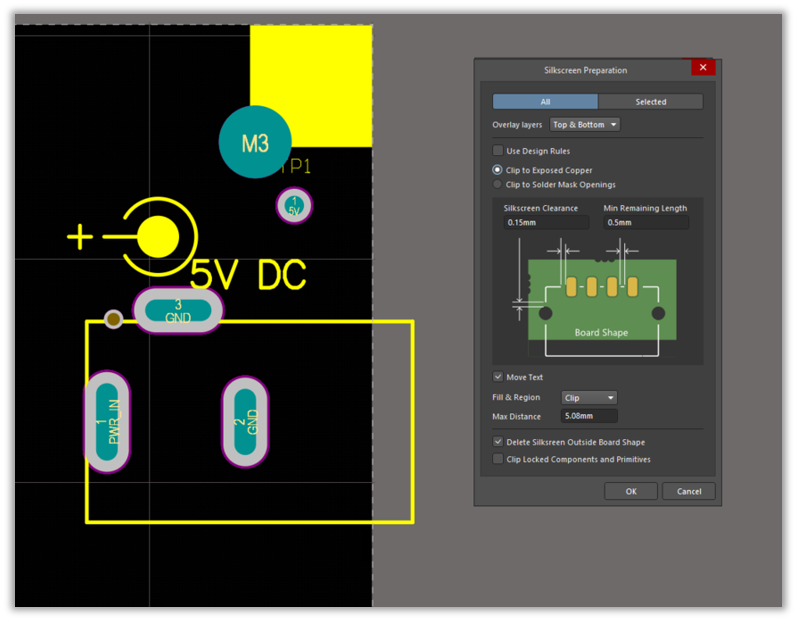

PCB 編輯器

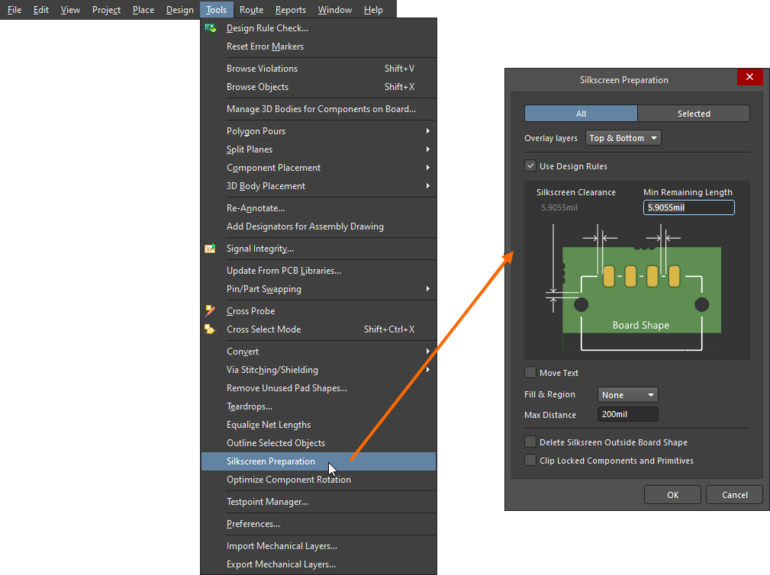

菜單欄下打開:【Tools】→【Silkscreen Preparation】,將絲印制備對話框打開。

圖 4

第一欄:設置即是將絲印制備適用于哪些元素對象的選擇,【All】選項為所有對象,【Selected】選項為僅在設計中選擇的對象,此處一般默認【All】適用于所有對象設置。

第二欄:Overlay layers 設置即為絲印制備命令執行的層范圍選擇,點擊下滑欄可以選擇單獨的【TOP】、【Bottom】或者【TOP&Bottom】選項,推薦默認設置為【TOP&Bottom】選項,讓其命令在頂底絲印層都可進行實現。

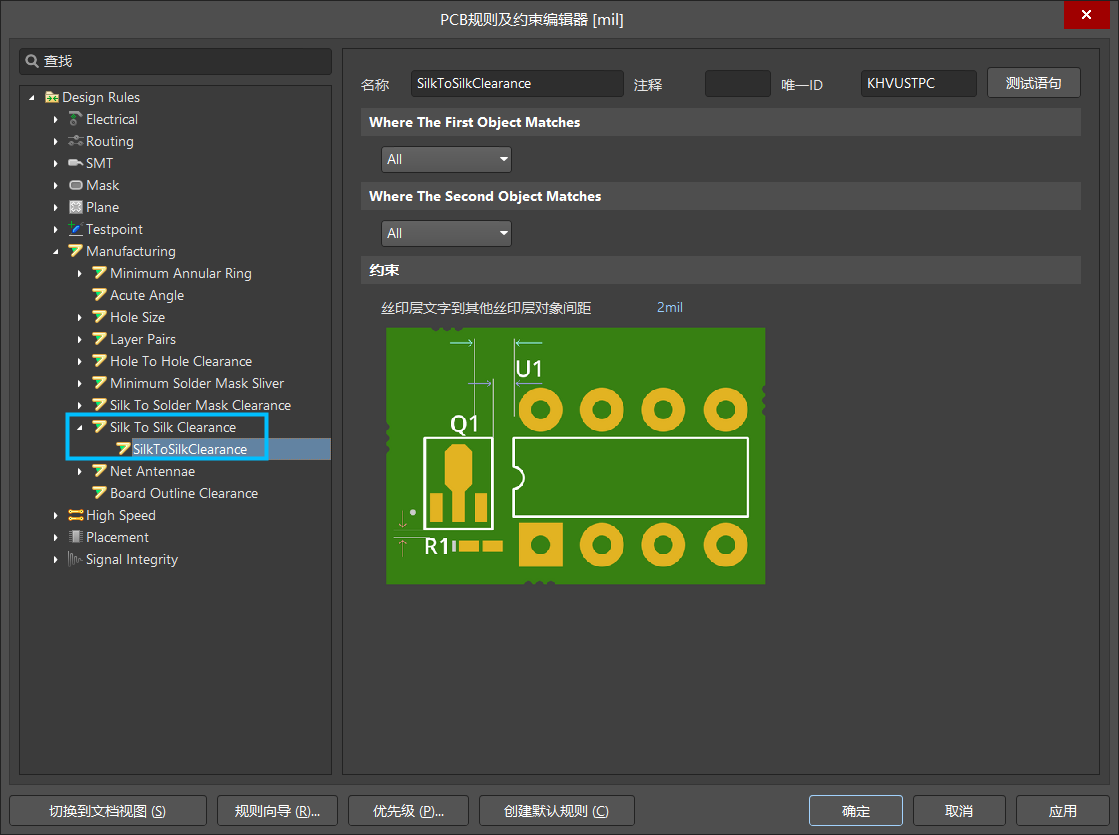

第三欄:勾選【Use Design Rules】選項,那么絲印制備則是按照【PCB規則及約束編輯器】對話框內的絲印跟絲印層對象間距規則進行執行。

圖 5

如果不勾選【Use Design Rules】選項,那么就需要根據 PCB 設計要求手動選擇絲印避讓的對象,兩種方式選擇:【Clip to Exposed Copper】、【Clip to solder Mask Openings】選擇銅層或者阻焊層的設置模式,可根據具體設計進行選擇,推薦設置為【Clip to solder Mask Openings】選擇完模式之后即可設置絲印間距,間距受【Max Distance】值的約束。

第四欄:勾選【Move Text】選項,一般在PCB設計完成之后是需要調整器件位號絲印不要覆蓋在焊盤上,所以需要將【Move Text】選項進行勾選,間距受【Max Distance】值的約束。

第五欄:【Fill & Region】在有Fill & Region情況下,可以選擇三種模式:

1、None 不做處理;2、Clip 進行裁剪;3、Move 進行移動,受【Max Distance】值的約束。

第六欄:【Delete Silksreen Outside Board Shape】選項即為是否需要自動移除板框外部的絲印。

第七欄:【Clip Locked Components ang Prinitives】選項即為絲印制備針對PCB設計中鎖定的器件是否實行變更

處理。

圖 6

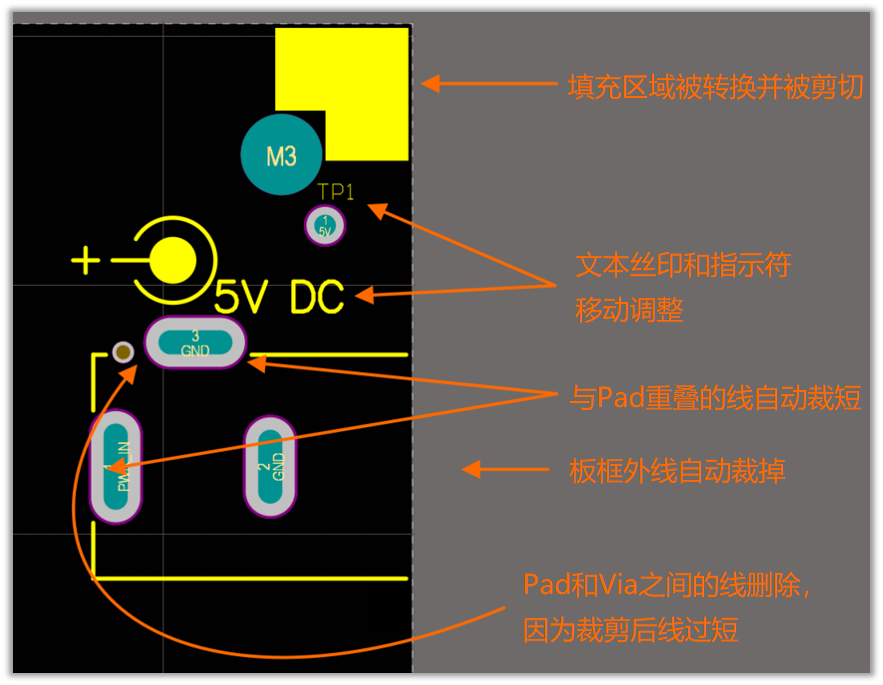

效果如下:

圖 7

首頁 > 資源中心 > FAQ

首頁 > 資源中心 > FAQ